Prototyping

Low Volume Production (LVP)

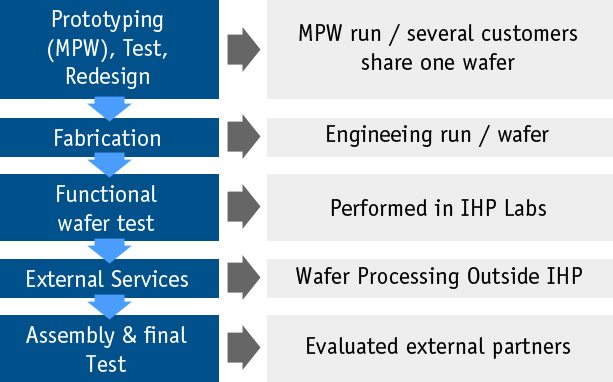

IHP's wafer fab unites the state-of-the-art research and SiGe BiCMOS technology. The production line offers various options to produce a few chips on a Multi-Project-Wafer (MPW) up to a couple of wafers as an engineering run. The wafer fab fits the needs of companies, international universities and research institutes that require a small number of samples for development and possibly later a higher number of chips for their product production.

MPW Runs

The MPW Runs are a cost efficient option for the production of a small number of ICs by sharing the wafer and masks with other projects. By default each customer receives 40 ICs per run. Larger amounts are also possible. MPW ICs can be used in the early phase of product development in order to test and optimize the chip design or structures before finalizing a fully functional ASIC.

Engineering Runs

An Engineering Run is a customer-specific manufacturing run, including a customer specific mask set. Within this mode six wafers are delivered to customers. The same mask set can be used for the low volume production run later.

The technical basis for the chip manufacturing is the high-tech SiGe BiCMOS fabrication line of IHP in a 1500 m² Class-3 clean room operating in 24/7 mode.

Key characteristics of the fabrication line are:

- toolset for 0.13 µm technology on 200 mm wafers

- cycle times down to two days per mask level